Toshiba

Memory Corporation, el líder mundial en soluciones de memoria, hoy

anunció el desarrollo de un chip puente que produce SSDs de alta

velocidad y gran capacidad. Usando los chips puentes desarrollados, con

una área pequeña ocupada y un bajo consumo de energía, la compañía ha

conseguido conectar más chips de memoria flash con menos líneas de señal

de alta velocidad que con el método convencional sin chips puente. El

resultado de este desarrollo fue anunciado en San Francisco el 20 de

febrero, en la International Solid-State Circuits Conference 2019 (ISSCC

2019).

Este comunicado de prensa trata sobre multimedia. Ver la noticia completa aquí:

https://www.businesswire.com/news/home/20190221006059/es/

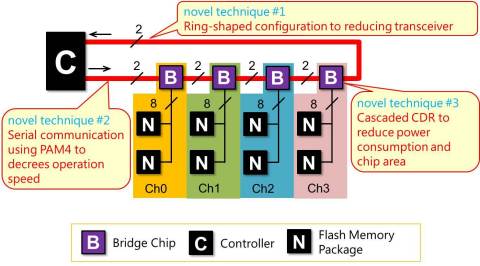

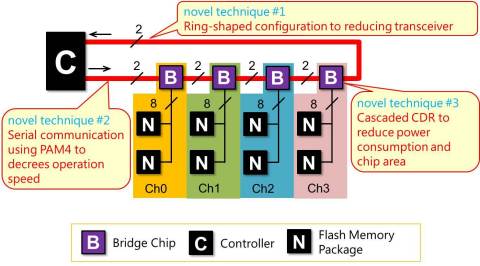

Fig. 1 Connection using bridge chips (Graphic: Business Wire)

En SSDs, los múltiples chips de memoria flash están conectados a un

controlador que administra su operación. A medida que más chips de

memoria flash son conectados a una interface del controlador, se va

degradando la velocidad de operación, por lo que hay restricciones a la

cantidad de chips que se pueden conectar. Para incrementar la capacidad,

es necesario incrementar la cantidad de interfaces, pero eso da como

resultado una enorme cantidad de líneas de señal de alta velocidad

conectadas al controlador, haciendo que sea más dificultoso implementar

el cableado en el panel SSD.

La compañía ha superado este problema con el desarrollo de un chip

puente que conecta los chips del controlador y de la memoria flash (Fig.

1), tres novedosas técnicas: una conexión encadenada*1 que

incluye los chips del controlador y los chips puente en forma de anillo;

una comunicación de serie que usa PAM 4*2; y una técnica de

mejoramiento de vibración*3 para eliminar un circuito PLL*4

en los chips puente. Aplicando estas técnicas se reduce la sobrecarga de

los chips puente, al tiempo que es posible operar una gran cantidad de

chips de memoria flash a alta velocidad con solo unas pocas líneas de

señal de alta velocidad (Fig. 2).

La configuración con forma de anillo de los chips puente y del

controlador reduce la cantidad de transceptores requeridos en el chip

puente de dos pares a un par, lo que permite una reducción del área del

chip puente. Además, adoptando comunicación en serie PAM 4 entre los

chips del controlador y del puente encadenado se baja la velocidad de

operación en los circuitos de los chips puente y se atenúa su

performance requerida. Un nuevo CDR*5 que utiliza los

atributos de PAM 4 para mejorar los problemas de vibración elimina la

necesidad de contar con un circuito PLL en el chip puente, lo que

también contribuye a requerir un área más pequeña para el chip y un

menor consumo de energía.

Los chips puente prototipos fueron fabricados con proceso de CMOS 28nm y

los resultados fueron evaluados conectando cuatro chips puente y un

controlador en un encadenado con forma de anillo. Esto confirmó

satisfactoriamente el desempeño de la comunicación PAM 4 vía todos los

chips puente y el controlador a 25,6 Gbps; asimismo, eso hace posible

obtener un BER*6 de menos de 10-12.

De aquí en adelante, la compañía continuará el trabajo de desarrollo en

pos de lograr almacenamiento a alta velocidad y de gran capacidad a

niveles aún no conocidos, mejorando la performance del chip puente y

reduciendo al mismo tiempo el área de chip y el consumo de energía.

Notas

*1 Cadena en serie: un esquema de conexión en el

cual múltiples chips son cableados juntos siguiendo una secuencia

*2

PAM 4: Modulación de amplitud de pulso en 4 niveles (contiene

información de valor 4)

*3 Vibración: Fluctuación en

forma de ondas del dominio del tiempo del reloj o señal

*4

PLL: Lazo de Seguimiento de Fase (un circuito que genera una señal de

referencia exacta)

*5 CDR: Recuperación de Datos del

Reloj (un circuito que recupera la información y el reloj desde la señal

recibida)

*6 BER: Tasa de error binario (el valor más

bajo corresponde a la mejor performance)

Acerca de Toshiba Memory Corporation

Toshiba Memory Corporation, un líder mundial de soluciones de memoria,

se dedica al desarrollo, la producción y la venta de memorias flash y

SSD. En junio de 2018, Toshiba Memory fue comprada por un consorcio

industrial dirigido por Bain Capital. Toshiba Memory es pionera en

soluciones y los servicios vanguardistas y pioneros de memoria que

enriquecen la vida de las personas y expanden los horizontes de la

sociedad. La innovadora tecnología de memoria flash 3D de la compañía,

BiCS FLASH™, está dando forma al futuro del almacenamiento en

aplicaciones de alta densidad, incluidos los smartphones de avanzada,

las PC, las unidades SSD, la industria automotriz y los centros de

datos. Para mayor información acerca de Toshiba Memory, sírvase visitar https://business.toshiba-memory.com/en-apac/top.html

El texto original en el idioma fuente de este comunicado es la versión

oficial autorizada. Las traducciones solo se suministran como adaptación

y deben cotejarse con el texto en el idioma fuente, que es la única

versión del texto que tendrá un efecto legal.

Vea la versión original en businesswire.com: https://www.businesswire.com/news/home/20190221006059/es/

Hardware

Hardware

Miércoles 24 de diciembre - 16:18

Miércoles 24 de diciembre - 16:18

Registrar

Registrar  Conectar

Conectar